# XDS510PP PLUS Parallel Port JTAG Emulator

## Installation Guide

# XDS510PP PLUS Parallel Port JTAG Emulator Installation Guide

504955-0001 Rev. C March 2005

SPECTRUM DIGITAL, INC.

12502 Exchange Dr., Suite 440 Stafford, TX. 77477

Tel: 281.494.4505 Fax: 281.494.5310

sales@spectrumdigital.com www.spectrumdigital.com

#### **IMPORTANT NOTICE**

Spectrum Digital, Inc. reserves the right to make changes to its products or to discontinue any product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

Spectrum Digital, Inc. warrants performance of its products and related software to current specifications in accordance with Spectrum Digital's standard warranty. Testing and other quality control techniques are utilized to the extent deemed necessary to support this warranty.

Please be aware that the products described herein are not intended for use in life-support appliances, devices, or systems. Spectrum Digital does not warrant nor is liable for the product described herein to be used in other than a development environment.

Spectrum Digital, Inc. assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does Spectrum Digital warrant or represent any license, either express or implied, is granted under any patent right, copyright, or other intellectual property right of Spectrum Digital, Inc. covering or relating to any combination, machine, or process in which such Digital Signal Processing development products or services might be or are used.

#### WARNING

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **TRADEMARKS**

Windows 98, Windows NT, Windows 2000, and Windows XP are registered trademarks of Microsoft Corp.

Code Composer Studio is a trademark of Texas Instruments

## Contents

| 1 |                                                                              | 1-           |

|---|------------------------------------------------------------------------------|--------------|

|   | Provides an overview of the XDS510PP PLUS along with the keys features.      |              |

|   | 1.0 Overview of the XDS510PP PLUS                                            | 1-           |

|   | 1.1 Key Features of the XDS510PP PLUS                                        | 1-           |

|   | 1.2 Key Items on the XDS510PP PLUS                                           | 1-           |

| 2 | 2 Installing the XDS510PP PLUS Parallel Port JTAG Emulator                   | 2-           |

|   | Lists the hardware and software you'll need to install the XDS510PP PLUS Par | rallel Port  |

|   | JTAG Emulator, and the installation procedure of the XDS510PP PLUS in your   |              |

|   | 2.1 What You'll Need                                                         |              |

|   | Hardware checklist                                                           |              |

|   | Software checklist                                                           |              |

|   | 2.2 Installing the XDS510PP PLUS Parallel Port JTAG Emulator                 |              |

|   | 2.2.1 XDS510PP PLUS Installation Checklist                                   |              |

|   | 2.3 XDS510PP PLUS LED                                                        | 2-           |

|   | 2.4. WAIT-IN-RESET                                                           | 2-           |

|   | 2.5. Using The PD Pin to Power The XDS510PP PLUS                             | 2-           |

| 3 | 3 Specifications For Your Target System's Connection to the Emulator         | 3-           |

|   | Contains information about connecting your target system to the XDS510PP P   | LUS Parallel |

|   | Port JTAG Emulator                                                           |              |

|   | 3.1 Designing Your Target System's Emulator Connector (14-pin Header)        |              |

|   | 3.2 Bus Protocol                                                             |              |

|   | 3.3 Emulator Cable Pod Logic                                                 |              |

|   | 3.4 Emulator Cable Pod Signal Timing                                         |              |

|   | 3.5 Buffering Signals Between the Emulator and the Target System             |              |

|   | 3.6 Emulation Timing Calculations                                            |              |

|   | 3.7 Mechanical Dimensions of the XDS510PP PLUS Parallel Port JTAG Emul       | ator 3-1     |

#### **About This Manual**

This document describes the module level operations of the XDS510PP PLUS Parallel Port JTAG Emulator. This emulator is designed to be used with digital signal processors (DSPs) and microcontrollers designed by Texas Instruments.

The XDS510PP PLUS Parallel Port JTAG Emulator is a table top module that attaches to a personal computer or laptop to allow hardware engineers and software programmers to develop applications with DSPs and microcontrollers.

#### **Notational Conventions**

This document uses the following conventions.

The XDS510PP PLUS Parallel Port JTAG Emulator will sometimes be referred to as the PP PLUS.

Program listings, program examples, and interactive displays are shown is a special italic typeface.

#### **Information About Cautions**

This book may contain cautions.

#### This is an example of a caution statement.

A caution statement describes a situation that could potentially damage your software, or hardware, or other equipment. The information in a caution is provided for your protection. Please read each caution carefully.

#### **Related Documents**

Texas Instruments Code Composer and Code Composer Studio Users Guide

## Chapter 1

# Introduction to the XDS510PP PLUS Parallel Port JTAG Emulator

This chapter provides you with a description of the XDS510PP PLUS Parallel Port JTAG Emulator along with the key features.

| Topic |                                   | Page |

|-------|-----------------------------------|------|

| 1.0   | Overview of the XDS510PP PLUS     | 1-2  |

| 1.1   | Key Features of the XDS510PP PLUS | 1-2  |

| 1.2   | Key Items on the XDS510PP PLUS    | 1-3  |

#### 1.0 Overview of the XDS510PP PLUS

The XDS510PP PLUS Parallel Port JTAG Emulator is designed to be used with digital signal processors (DSPs) and microprocessors which operate between +3.3 volts to +5 volts. This emulator is powered from the PD pin on the target JTAG connector or from an external power supply which is included with the emulator.

The XDS510PP PLUS is designed to be compatible with the existing Texas Instruments XDS510 emulator and operate with debuggers provided by Texas Instruments.

#### 1.1 Key Features of the XDS510PP PLUS

The XDS510PP PLUS Parallel Port JTAG Emulator has the following features:

- Supports Texas Instrument's Digital Signal Processors and Microcontrollers with JTAG interface (IEEE 1149.1)

- Compatible with Texas Instrument's XDS510 emulator.

- Advanced emulation controller provides high performance.

- Supports standard parallel communication interface with host PC (SPP8, EPP, and ECP). No adapter required.

- Supports JTAG interfaces from +3.3-5 volts.

- One status LED for operational status.

- Incorporates EMU0/EMU1 Wait-In-Reset features for TMS27xx DSPs.

- · Power provided by target or power supply.

- Compatible with Texas Instruments Code Composer Studio

#### 1.2 Key Items on the XDS510PP PLUS

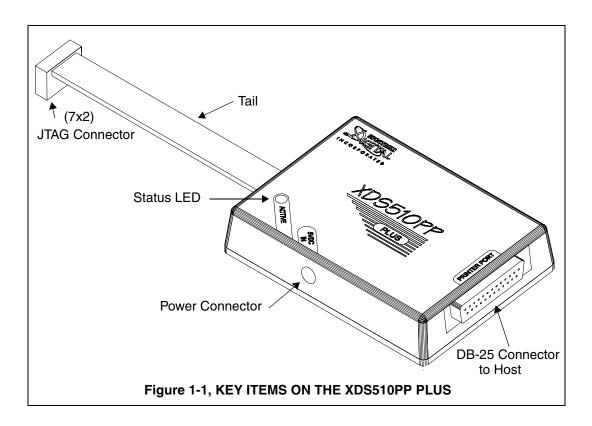

Figure 1-1 shows the XDS510PP PLUS. The key items identified are:

- Status LED

- JTAG connector

- Tail

- DB-25 connector to the host adapter card

- Power connector

### Chapter 2

# Installing the XDS510PP PLUS Parallel Port JTAG Emulator

This chapter helps you install the XDS510PP PLUS Parallel Port JTAG Emulator. For use with specific software packages such as the Code Composer/Studio refer to the documentation on that product.

| Topic |                                                 | Page |

|-------|-------------------------------------------------|------|

| 2.1   | What You'll Need                                | 2-2  |

|       | Hardware checklist                              | 2-2  |

|       | Software checklist                              | 2-2  |

| 2.2   | Installing the XDS510PP PLUS Parallel Port JTAG | 2-3  |

|       | Emulator                                        |      |

| 2.2.1 | XDS510PP PLUS Installation Checklist            | 2-3  |

| 2.3   | XDS510PP PLUS LED                               | 2-5  |

| 2.4   | WAIT-IN-RESET                                   | 2-5  |

| 2.5   | Using The PD Pin to Power The XDS510PP PLUS     | 2-5  |

#### 2.1 What You'll Need

The following checklists detail items that are shipped with the XDS510PP PLUS and additional items you'll need to use these tools.

#### Hardware checklist

| host            | An IBM PC/AT or 100% compatible PC or laptop with a hard-disk system and a CD-ROM drive with SPP8, EPP, or ECP compatible parallel port |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| memory          | Minimum of 32MB                                                                                                                         |

| display         | Color VGA or LCD                                                                                                                        |

| emulator module | XDS510PP PLUS Parallel Port JTAG emulator with power supply                                                                             |

| target system   | A board with a TI DSP or Microcontroller and power supply                                                                               |

| connector to    | 14-pin connector (two rows of seven pins) see Chapter 3 for                                                                             |

#### Software checklist

| <br>operating system | Win 98, Win NT 4.0, Win 2000, or Win XP              |

|----------------------|------------------------------------------------------|

| <br>software tools   | Compiler/assembler/linker for DSP or Microcontroller |

| <br>debugger         | Code Composer Studio                                 |

| <br>drivers t        | drivers for Code Composer/Code Composer Studio       |

<sup>&</sup>lt;sup>t</sup> Included as part of the XDS510PP PLUS package

#### 2.2 Installing the XDS510PP PLUS Parallel Port JTAG Emulator

This section contains the steps for installing the XDS510PP PLUS Parallel Port JTAG Emulator.

#### **WARNING**

Target Cable Connectors:

Be very careful with the target cable connectors. connect them gently; don't force them into position, or you may damage the connectors.

Do **not** connect or disconnect the DB-25 connector while the PC is powered up.

Do **not** connect or disconnect the 14-pin cable while the target system is powered up.

#### 2.2.1 XDS510PP PLUS Installation Checklist

| To install the XDS510PP PLUS execute the following checklist:                                                |

|--------------------------------------------------------------------------------------------------------------|

| ☐ Turn off the power to your PC or laptop                                                                    |

| ☐ Turn off the power to your target system (DSP or microcontroller system)                                   |

| ☐ Attach the XDS510PP PLUS DB-25 connector to the parallel port on the PC or laptop with the supplied cable. |

| ☐ If the target is supplying 3.3 volts on the PD pin of the JTAG connector:                                  |

| plug the power supply for the XDS510PP PLUS emulator into the emulator.                                      |

| plug the power supply for the XDS510PP PLUS emulator into a 110/220 VAC outlet.                              |

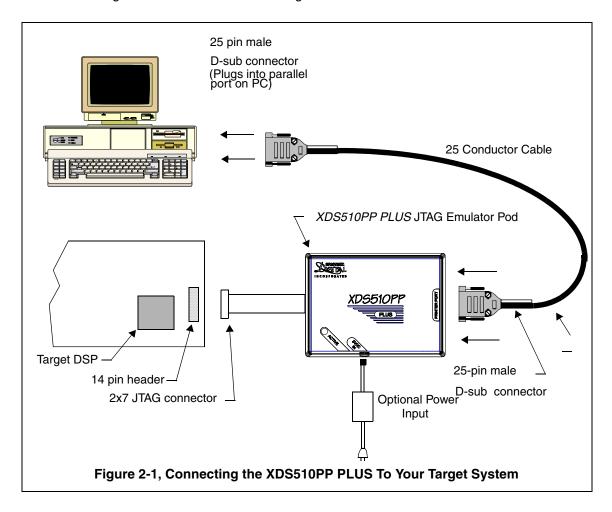

| ☐ Your system configuration should now look like that in Figure 2.1                                          |

| ☐ Apply power to your target.                                                                                |

| ☐ Apply power to your PC or laptop.                                                                          |

Figure 2-1 shows how you connect the XDS510PP PLUS in a typical system configuration with a host PC and target board.

#### 2.3 XDS510PP PLUS LED

The XDS510PP PLUS has 1 red Light Emitting Diode (LED). This LED indicates a connect has been made to the target system.

#### 2.4 WAIT-IN-RESET

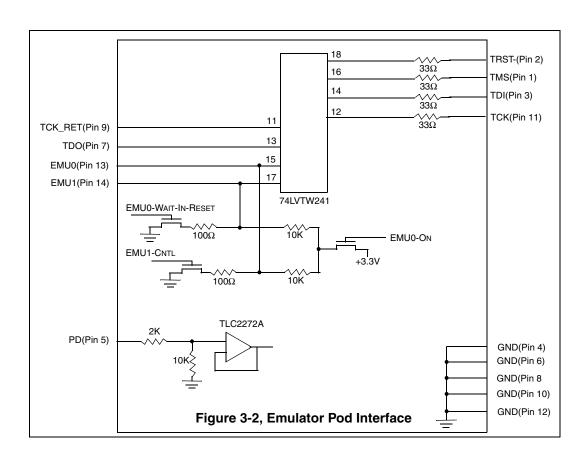

Newer TI DSPs (e.g. TMS320C27x) have a feature called Wait-In-Reset. When the XDS510PP PLUS detects the loss of target poser it will drive EMU0 to 0 volts. When the target system is powered on and EMU0 = 0 volts, EMU1 = Vcc, and TRSTn = 0 volts then the DSP will wait in reset until the debugger is started. On processors that do not support Wait-In-Reset" pulling EMU0 should have no effect. EMU0 is tri-stated within 20 milliseconds after TRST returns high. A 100 ohm resistor is included in the event that the target system is driving this signal. Normally this signal is pulled high on the target system with a 4.7K ohm or larger resistor.

#### 2.5 Using The PD Pin to Power The XDS510PP PLUS

When the XDS510PP PLUS is powered by the target system, the PD pin on the JTAG connector must be tied directly to +5 volts. The XDS510PP PLUS consumes 250 Ma. from the target system. This means the designer of the target system must allow for this extra power consumption if the XDS510PP PLUS is to be powered by the target. When the external power supply connection is used, the emulator draws no power from the target.

## Chapter 3

# **Specifications For Your Target System's Connection to the Emulator**

This chapter contains information about connecting your target system to the emulator. Your target system must use a special 14-pin connector for proper communication with the emulator.

|                                                                                  | Page                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Designing Your Target System's Emulator                                          |                                                                                                                                                                                                                                        |

| Connector (14-pin Header)                                                        | 3-2                                                                                                                                                                                                                                    |

| Bus Protocol                                                                     | 3-3                                                                                                                                                                                                                                    |

| Emulator Cable Pod Logic                                                         | 3-4                                                                                                                                                                                                                                    |

| Emulator Cable Pod Signal Timing                                                 | 3-5                                                                                                                                                                                                                                    |

| Buffering Signals Between the Emulator and the<br>Target System                  | 3-6                                                                                                                                                                                                                                    |

| Emulation Timing Calculations                                                    | 3-9                                                                                                                                                                                                                                    |

| Mechanical Dimensions of the XDS510PP PLUS Parallel Port Scan Path Interface Pod | 3-11                                                                                                                                                                                                                                   |

|                                                                                  | Connector (14-pin Header) Bus Protocol Emulator Cable Pod Logic Emulator Cable Pod Signal Timing Buffering Signals Between the Emulator and the Target System Emulation Timing Calculations Mechanical Dimensions of the XDS510PP PLUS |

#### 3.1 Designing Your Target System's Emulator Connector (14-pin Header)

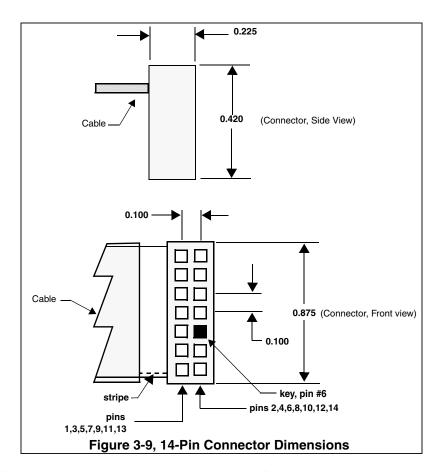

Certain devices support emulation through a dedicated emulation port. This port is a superset of the IEEE 1149.1 (JTAG) standard and is accessed by the emulator. To perform emulation with the emulator, your target system must have a 14-pin header 2 rows of 7 pins) with the connections that are shown in Figure 3-1. Table 1 describes the emulation signals.

| TMS                                              | 1  | 2  | TRST-        |                                     |

|--------------------------------------------------|----|----|--------------|-------------------------------------|

| TDI                                              | 3  | 4  | GND          | Header Dimensions                   |

| PD                                               | 5  | 6  | no pin (key) | Pin-to-Pin spacing, 0.100 in. (X,Y) |

| TDO                                              | 7  | 8  | GND          | Pin width, 0.025-in. square post    |

| TCK-RET                                          | 9  | 10 | GND          | Pin length, 0.235-in. nominal       |

| TCK                                              | 11 | 12 | GND          |                                     |

| EMU0                                             | 13 | 14 | EMU1         |                                     |

| Figure 3-1, 14 Pin Header Signals and Dimensions |    |    |              |                                     |

**Table 1: 14-Pin Header Signal Description**

| Signal  | Description                                                                                                                                                   | Emulator<br>State | Target<br>State |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|

| TMS     | JTAG test mode select.                                                                                                                                        | Output            | Input           |

| TDI     | JTAG test data input.                                                                                                                                         | Output            | Input           |

| TDO     | JTAG test data output.                                                                                                                                        | Input             | Output          |

| тск     | JTAG test clock. TCK is a 10-MHz clock source from the emulation pod. This signal can be used to drive the system test clock.                                 | Output            | Input           |

| TRST-   | JTAG test reset.                                                                                                                                              | Output            | Input           |

| EMUO    | Emulation pin 0.                                                                                                                                              | I/O               | I/O             |

| EMU1    | Emulation pin 1.                                                                                                                                              | I/O               | I/O             |

| PD      | Presence detect. Indicates that the emulation cable is connected and that the target is powered up. PD should be tied to the target processor's I/O pins Vcc. | Input             | Output          |

| TCK_RET | JTAG test clock return. Test clock input to the emulator. May be a buffered or unbuffered version of TCK.                                                     | Input             | Output          |

Although you can use other headers, recommended parts include:

straight header, unshrouded DuPont Connector Systems

part # 67996-114

right-angle header, unshrouded DuPont Connector Systems

part # 68405-114

#### 3.2 Bus Protocol

The IEEE 1149.1 specification covers the requirements for JTAG bus slave devices (such as the TMS320C5x family) and provides certain rules, summarized as follows:

\_\_ The TMS/TDI inputs are sampled on the rising edge of the TCK signal of the device.

\_\_ The TDO output is clocked from the falling edge of the TCK signal of the device

When JTAG devices are daisy-chained together, the TDO of one device has approximately a half TCK cycle set up to the next device's TDI signal. This type of timing scheme minimizes race conditions that would occur if both TDO and TDI were timed from the same TCK edge. The penalty for this timing scheme is a reduced TCK frequency.

The IEEE 1149.1 specification does not provide rules for JTAG bus master (emulator) devices.

#### 3.3 Emulator Cable Pod Logic

Figure 3-2 shows a portion of the emulator cable pod. These are the functional features of the emulator pod:

- Signals TMS and TDI are generated from the rising edge of TCK\_RET.

- Signals TMS, TDI, TCK, and TRST- are series-terminated to reduce signal reflections.

- A 10-MHz test clock source is provided. You may also provide your own test clock for greater flexibility.

#### 3.4 Emulator Cable Pod Signal Timing

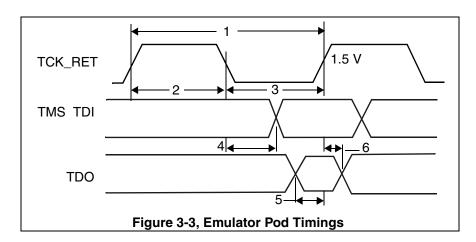

Figure 3-3 shows the signal timings for the emulator. Table 2 defines the timing parameters for the emulator. The timing parameters are calculated from standard data sheet parts used in the emulator and cable pod. These parameters are for reference only. Spectrum Digital does not test or guarantee these timings. The emulator pod uses TCK\_RET as its clock source for internal synchronization. TCK is provided as an optional target system test clock source.

**Table 2: Emulator Pod Timing Parameters**

| No | Reference                | Description                     | Min | Max   | Units |

|----|--------------------------|---------------------------------|-----|-------|-------|

| 1  | t <sub>TCKmin</sub>      | TCK_RET period                  | 50  | 10000 | ns    |

| 2  | t <sub>TCKhighmin</sub>  | TCK_RET high pulse duration     | 15  |       | ns    |

| 3  | t <sub>TCKlowmin</sub>   | TCK_RET low pulse duration      | 15  |       | ns    |

| 4  | $td_{(XTMX)}$            | TMS/TDI valid from TCK_RET low  | 5   | 22    | ns    |

| 5  | tsu <sub>(XTDOmin)</sub> | TDO setup time to TCK_RET high  | 5   |       | ns    |

| 6  | thd <sub>(XTDOmin)</sub> | TDO hold time from TCK_RET high | 5   |       | ns    |

#### 3.5 Buffering Signals Between the Emulator and the Target System

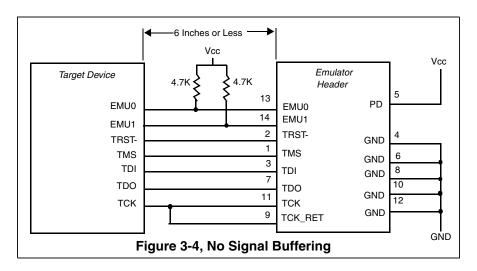

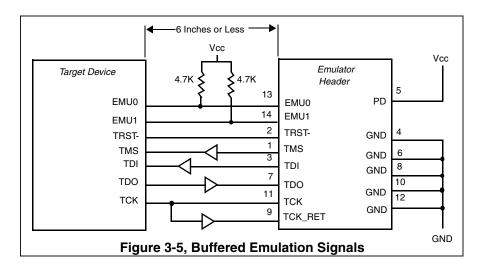

It is extremely important to provide high-quality signals between the emulator and the target device on the target system. If the distance between the emulation header and the target device is greater than 6 inches, the emulation signals must be buffered. The need for signal buffering and placement of the emulation header can be divided into two categories:

No signal buffering. As shown in figure 3-4, the distance between the header and the target device should be no more than 6 inches.

\_\_ Buffered emulation signals. Figure 3-5 shows the distance between the emulation header and the target device is greater than 6 inches. The target device signals--TMS, TDI, TDO, and TCK\_RET are buffered through the same package.

- The EMU0 and EMU1 signals must have pullups to Vcc. The pullup resistor value should be chosen to provide a signal rise time less than 10 uS. A 4.7k ohm resistor is suggested for most applications. EMUO-1 are I/O pins on the target device, however, they are only inputs to the emulator. In general, these pins are used in multiprocessor systems to provide global run/stop operations.

- It is extremely important to provide high quality signals, especially on the processor TCK and the emulator TCK\_RET signal. In some cases, this may require you to provide special PWB trace routing and to use termination resistors to match the trace impedance. The emulator pod does provide fixed series termination on the TMS, TCK, and TDI signals.

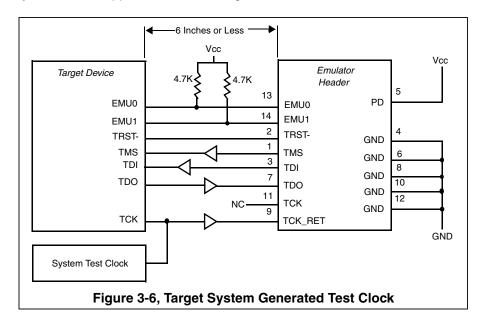

Figure 3-6 shows an application with the system test clock generated in the target system. In this application the TCK signal is left unconnected.

There are two benefits to having the target system generate the test clock:

- The emulator provides only a single 10-MHz test clock. If you generate your own test clock, you can set the frequency to match your system requirements.

- \_\_ In some cases, you may have other devices in your system that require a test clock when the emulator is not connected.

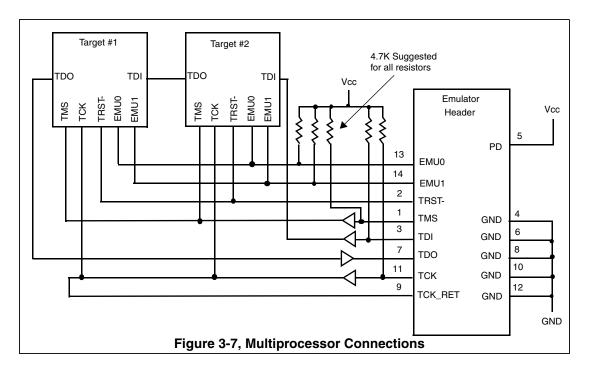

Figure 3-7 shows a typical multiprocessor configuration. This is a daisy chained configuration (TDO-TDI daisy-chained), which meets the minimum requirements of the IEEE 1149.1 specification. The emulation signals in this example are buffered to isolate the processors from the emulator and provide adequate signal drive for the target system. One of the benefits of a JTAG test interface is that you can generally slow down the test clock to eliminate timing problems. Several key points to multiprocessor support are as follows:

- \_\_ The processor TMS, TDI, TDO, and TCK should be buffered through the same physical package to better control timing skew.

- The input buffers for TMS, TDI, and TCK should have pullups to Vcc. This will hold these signals at a known value when the emulator is not connected. A pullup of 4.7k ohms is suggested.

#### 3.6 Emulation Timing Calculations

The following are a few examples on how to calculate the emulation timings in your system. For actual target timing parameters, see the appropriate device data sheets.

#### **Assumptions:**

| $t_{su(TTMS)}$          | Target TMS/TDI setup to TCK high                                                                          | 5  | ns  |

|-------------------------|-----------------------------------------------------------------------------------------------------------|----|-----|

| t <sub>h(TTMS)</sub>    | Target TMS/TDI hold from TCK high                                                                         | 5  | ns  |

| $t_{d(TTDO)}$           | Target TDO delay from TCK low                                                                             | 10 | ns  |

| t <sub>d(bufmax)</sub>  | Target buffer delay maximum                                                                               | 7  | ns  |

| t <sub>d(bufmin</sub> ) | Target buffer delay minimum                                                                               | 1  | ns  |

| <sup>t</sup> (bufskew)  | Target buffer skew between two devices in the same package: $[t_{d(bufmax)} - t_{d(bufmin)}] \times 0.15$ | .9 | ns  |

| t <sub>tckfactor</sub>  | Assume a 40/60 duty cycle clock                                                                           |    | 0.4 |

#### Given in Table 2:

| t <sub>d(XTMSmax)</sub> | Emulator TMS/TDI delay from TCK_RET high, max |   | ns |

|-------------------------|-----------------------------------------------|---|----|

| $t_{su(XTDOmin)}$       | TDO setup time to emulator TCK_RET high       | 5 | ns |

There are two key timing paths to consider in the emulation design:

```

the TCK_RET/TDI(tprdtck_TMS) path, and

the TCK_RET/TDO(tprdtck_TDO) path.

```

In each case, the worst case path delay is calculated to determine the maximum system test clock frequency.

Case 1: Single processor, direct connection, TMS/TDI timed from TCK\_RET.

$$\begin{array}{ll} t_{prdtck\_TMS} & = (t_{d(XTMSmax)} + t_{su(TTMS)}) \ ^* \ 2 \\ & = (22ns + 5ns) \ ^* \ 2 \\ & = 54ns \ (18.5 \ MHz) \\ \\ t_{prdtck\_TDO} & = [t_{d(TTDO)} + t_{su(XTDOmin)}] \ / \ t_{tckfactor} \\ & = (10ns + 5ns) \ / \ 0.4 \\ & = 37.5ns \ (26.6 \ MHz) \end{array}$$

In this case, the TCK/TMS-TDI path is the limiting factor.

**Case 2:** Single/multiple processor, TMS/TDI buffered input; TCK\_RET/TDO buffered output, TMS/TDI timed from TCK\_RET.

$$\begin{array}{ll} t_{prdtck\_TMS} &= \left(t_{d(XTMSmax)} + t_{su(TTMS)} + 2t_{d(bufmax)}\right) \ ^* \ 2 \\ &= \left(22ns + 5ns + 2(7ns)\right) \ ^* \ 2 \\ &= 82ns \ (12.2 \ MHz) \\ \\ t_{prdtck\_TDO} &= \left(t_{d(TTDO)} + t_{su(XTDOmin}\right) + t_{bufskew}\right) \ / \ t_{tckfactor} \\ &= \left(10ns + 5ns + 0.9 \ ns\right) \ / \ 0.4 \\ &= 39.8ns \ (25.1 \ MHz) \end{array}$$

In this case, the TCK/TMS-TDI path is the limiting factor.

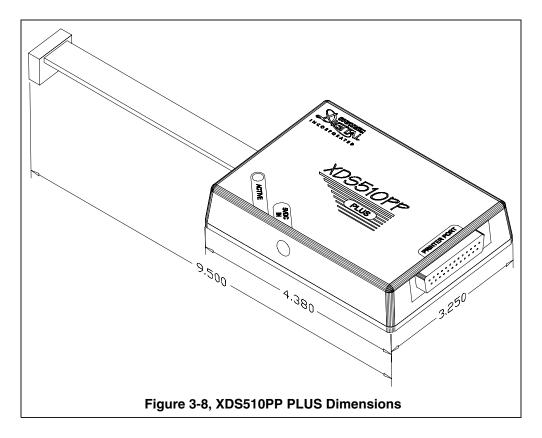

#### 3.7 Mechanical Dimensions of the XDS510PP PLUS Parallel Port JTAG Emulator

The XDS510PP PLUS Parallel Port Scan Path Interface Pod consists of a 6-foot 25 conductor cable, the **XDS510PP PLUS** emulator pod, and a short section of cable that connects to the target system. The overall cable length is approximately 6 feet, 10 inches. Figure 3-8 and Figure 3-9 (page 3-12) show the mechanical dimensions for the **XDS510PP PLUS** emulator pod and short cable. Note that the pin-to-pin spacing on the connector is 0.100 inches in both the X and Y planes. The **XDS510PP PLUS** enclosure is nonconductive plastic with four recessed metal screws.

Note: All dimensions are in inches and are nominal dimensions, unless otherwise specified.

Note: All dimensions are in inches and are nominal dimensions, unless otherwise specified.